In embedded systems, whenever communication is required between microcontrollers operating at different supply voltages—or between a microcontroller and peripheral chips with differing voltage levels—level shifting becomes an unavoidable necessity. Failure to implement such conversion will result in communication failures or, worse, voltage levels exceeding the microcontroller's tolerance limits, potentially causing permanent damage. The following section outlines five mainstream solutions for level shifting.

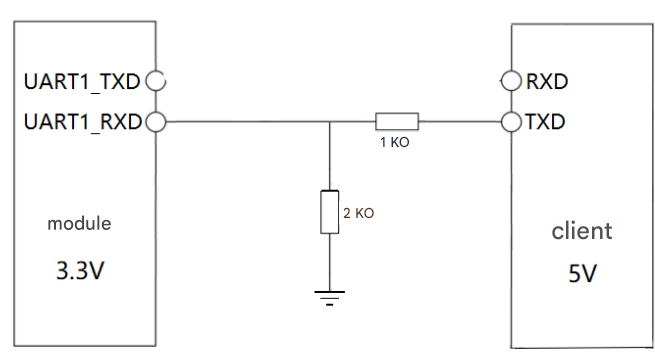

1. Resistive Voltage Divider Solution

As shown in the figure above, the left side represents a 3.3V system, while the right side represents a 5V system. When a 5V-level client on the right sends data to the left, the voltage is divided across two resistors; the voltage at the receiving end on the left becomes approximately 5V × 2kΩ / (1kΩ + 2kΩ) ≈ 3.3V, thereby achieving voltage level matching.

Since this solution relies solely on resistors, its advantages are extremely low cost and ease of layout. However, its disadvantages are equally apparent: on one hand, power consumption is relatively high; on the other, its driving capability is limited, and it cannot operate at high speeds—typically, it is suitable only for frequencies below 100 kHz.

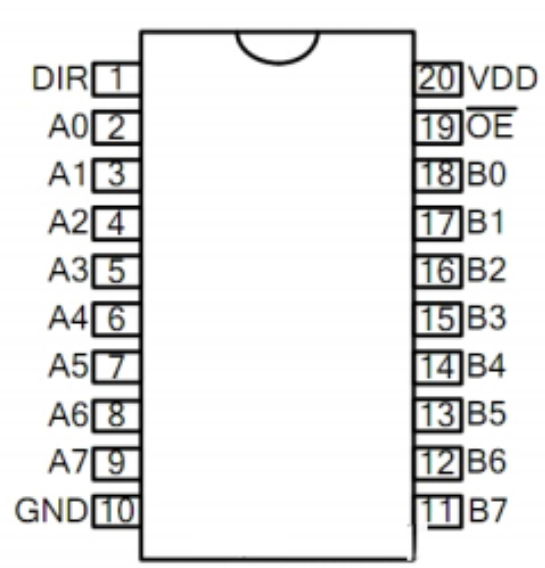

2. Level Shifter Chip Solution

By utilizing dedicated level shifter chips—such as those in the 74xHC and 74xHCT series—level conversion is performed internally within the chip; one simply needs to supply different voltages to the respective sides of the chip. This approach enables the bidirectional level conversion of seven channels between 3.3V and 5V.

Directly utilizing dedicated chips for level shifting offers several advantages: strong drive capability (thanks to CMOS output technology), low leakage current, suitability for multi-channel level translation, and high operating speeds. Its primary drawback, however, is the higher cost.

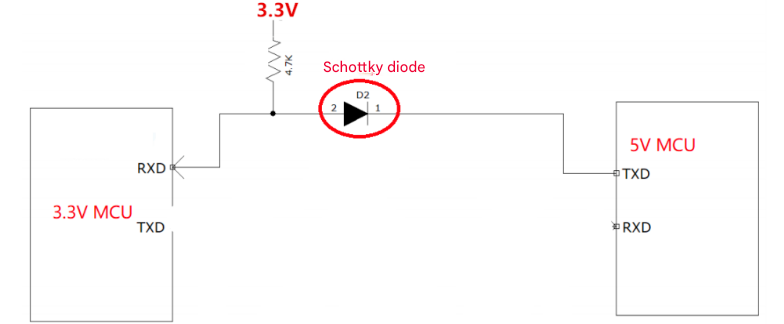

3. Diode-based Solution

Level shifting can also be achieved by utilizing the voltage drop across a diode for clamping purposes. As illustrated in the figure above, when the TXD pin of the 5V microcontroller on the right side outputs a high level, diode D2 is cut off; consequently, the RXD pin on the left side receives a high level of 3.3V via a pull-up resistor. Conversely, when the TXD pin of the microcontroller on the right side is at a low level, the clamping action of the diode causes the RXD pin on the left side to settle at approximately 0.3V, which is interpreted as a low level. Implementing this circuit requires D2 to have an exceptionally low forward voltage drop (<0.5V)—typically necessitating the use of a Schottky diode—otherwise, the logic levels on the left and right sides will fail to remain consistent.

The advantages of the diode-based solution include low leakage current and low cost; however, its disadvantages lie in the stringent requirement regarding the diode's forward voltage drop, as well as its relatively limited driving capability and data transmission speed.

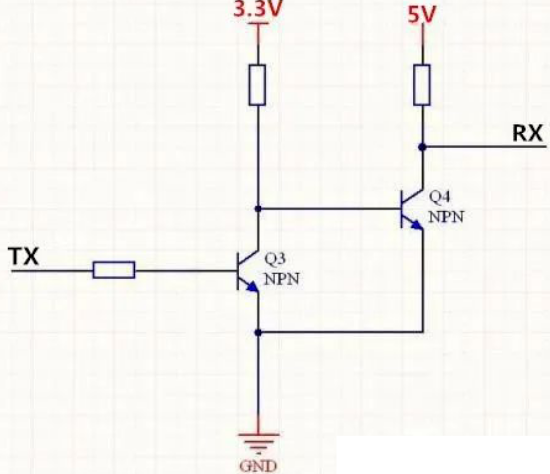

4. Transistor-based Solution

The circuit shown above utilizes two NPN transistors to convert a 3.3V input signal level into a 5V output level, while maintaining signal synchronization. Circuit Description: When TX is low, Q3 is off and Q4 is on; consequently, RX is pulled to ground and is also low. When TX is high, Q3 is on and Q4 is off; consequently, RX is pulled up to 5V. In this manner, the high and low states of both signals remain synchronized, and the voltage level conversion is successfully achieved.

The advantages of this circuit include low cost, strong driving capability, and a mature, widespread history of application. Its disadvantage is that the signal waveform experiences a delay during the transistor-based conversion process; therefore, the operating speed cannot be excessively high (the baud rate should not exceed 230,400). Furthermore, when implementing multi-channel conversion, the component count increases significantly, necessitating a larger layout area.

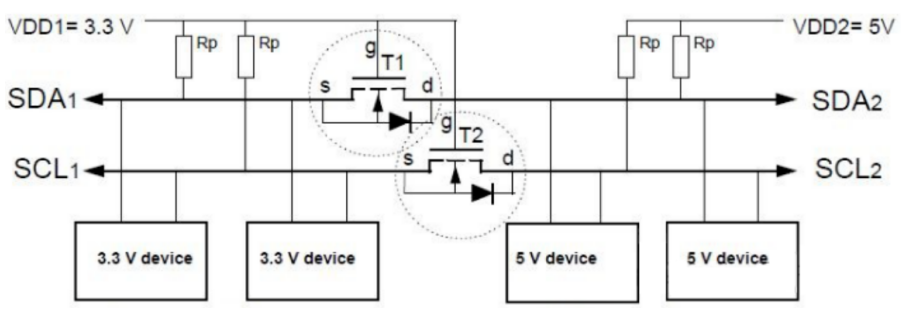

5. MOSFET-based Solution

The figure above illustrates a classic circuit utilizing a MOSFET to perform 5V-to-3.3V level shifting for I²C communication. Circuit Description: When SDA1 is high, there is no voltage drop across the MOSFET's Gate-Source terminals; consequently, the MOSFET remains non-conducting, and both SDA1 and SDA2 register as high logic levels—though their respective voltages remain independent. Conversely, when SDA1 is low, the MOSFET turns on, causing both SDA1 and SDA2 to register as low logic levels. The logical analysis for the SCL line is analogous to that of the SDA line.

This solution is suitable for the level shifting of low-frequency signals; it is cost-effective, exhibits a lower voltage drop compared to bipolar junction transistors (BJTs), and typically operates at speeds below 400 kHz.

Share